CHÉM GIÓ, BÀN LUẬN VỀ KỸ THUẬT

Lập trình STM32F4 - Phần 7: Lý thuyết GPIO

12 Tháng Năm 2021

Trong những phần hướng dẫn lập trình hệ thống nhúng với STM32F4 lần trước tôi đã đưa bạn đi qua các bước cần thiết trước khi viết chương trình và test các chức năng của chip. Lần này tôi sẽ giới thiệu cho các bạn phần lý thuyết về về GPIO của STM32F4, phục vụ cho một trong những chức năng cơ bản nhất của một con chip chính là điều khiển các chân của nó. Bài viết này chủ yếu dựa vào lý thuyết được trình bày trong Reference Manual của dòng chip STM32F407. Cũng không qua bài viết này mong rằng các bạn sẽ có thêm kinh nghiệm trong việc đọc datasheet của nhà sản xuất.

Giới thiệu

Đầu tiên GPIO là viết tắt của General-purpose I/O, Hiểu đơn giản nào các chân IO của STM32F4 có thể được sử dụng với những mục đích cơ bản tùy theo cấu hình như Input, Output, Analog hoặc chân chức năng cho các chuẩn điều khiển hoặc chuẩn truyền thông.

Các tính năng cơ bản:

- 16 I/Os được điều khiển cùng lúc trên 1 port

- Trạng thái đầu ra: push-pull hoặc open drain + pull-up/down

- Trạng thái đầu vào: floating, pull-up/down, analog

- Có thể lựa chọn tốc độ tối đa cho mỗi chân I/O

- Có thanh cho phép set và reset bit nhanh chóng.

- Cơ chế khóa được cung cấp để tránh việc thay đổi cấu hình I/O khi không được cho phép

- Chức năng tương tự

- Thanh ghi lựa chọn chức năng input/output thay thế (tối đa 16 AFs cho mỗi I/O)

- Có khả năng đổi trạng thái bit hay pin nhanh chóng trong hai chu kỳ clock

- Ghép kênh chân cực linh hoạt cho phép sử dụng các chân I/O làm GPIO hoặc một trong số các chức năng ngoại vi

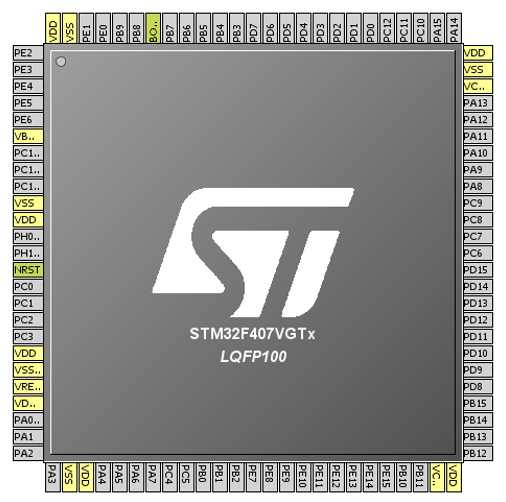

Đối với các dòng STM32 thì mỗi Port có 16 chân IO. Ở STM32F407VGTx có 5 port từ A, B, C, D, E và 2 chân PH0, PH1.

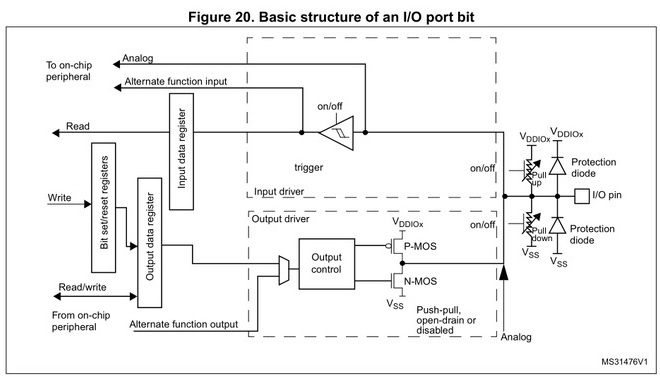

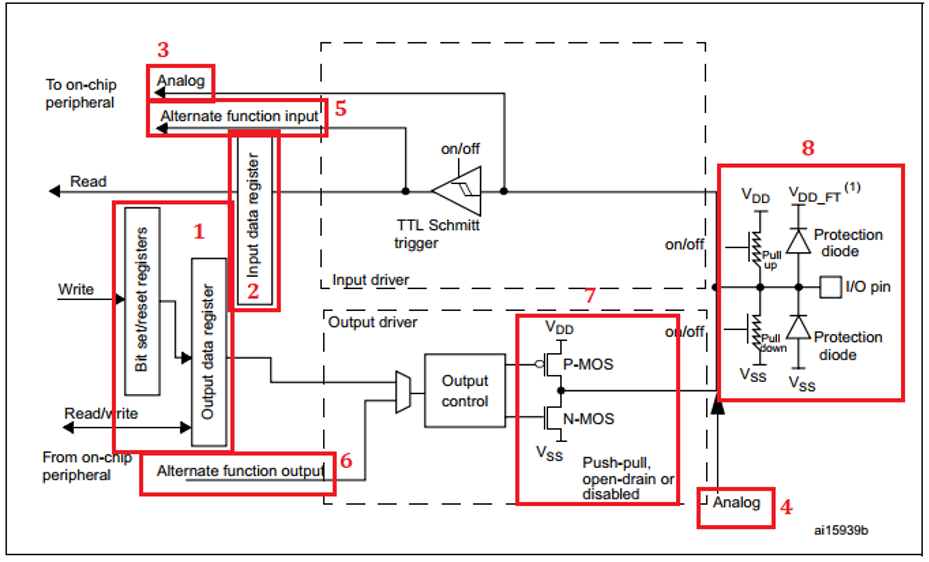

Dưới đây là kiến trúc cơ bản của một pin được thiết kế trong STM32F4

- Khu vực số 1: khi một chân IO được cấu hình là Output, giá trị ngõ ra của nó nó được điều khiển tùng bit bởi Bit set/reset registers, Giá trị ngõ ra thực sự sẽ được chứa trong Output data register, giá trị này có thể được đọc và ghi một cách trực tiếp.

- Khu vực số 2: khi bạn set giá trị cho chân Output chẳng hạn, thì giá trị thực sự bên ngoài sẽ được đọc và lưu trong Input data register, bạn chỉ cần đọc giá trị trong thanh ghi này để xác nhận status thực sự của pin. Nó sẽ hữu hiệu trong trường hợp ở bên ngoài có một tín hiệu khác tác động lên trên IO làm thay đổi giá trị được set cho output, hoặc là bạn chỉ muốn đọc giá trị bên ngoài của chân IO khi nó là Input.

- Khu vực số 3: khi chân IO của bạn được cấu hình là Analog Input, giá trị Analog này được động trực tiếp từ pin và đẩy thẳng cho Peripheral ADC để xử lý.

- Khu vực số 4: ngược lại, khi chân IO của bạn được cấu hình là Analog Output, giá trị ngõ ra được truyền thẳng vào chân IO.

- Khu vực số 5: khi IO được cấu hình là Alternate function ở chế độ Input, giá trị của pin sẽ được đọc sau đó thông qua Bộ TTL Schmitt trigger trước khi được đưa tới ngoại vi để xử lý.

- Khu vực số 6: ngược lại với khu vực 5, khi chân IO được cấu hình ở chế độ Output, giá trị muốn xuất ra của pin sẽ được chuyển thẳng vào Output control.

- Khu vực số 7: Đây là phần điện tử thử để giúp pin có thể được cấu hình theo các mode push-pull hoặc open drain hoặc không sử dụng 2 mode này.

- Khu vực số 8: giúp chân IO có thể được cấu hình ở dạng pull-up/down và đi-ốt bảo vệ có tác dụng tránh các tín hiệu gây tổn hại đến chân IO.

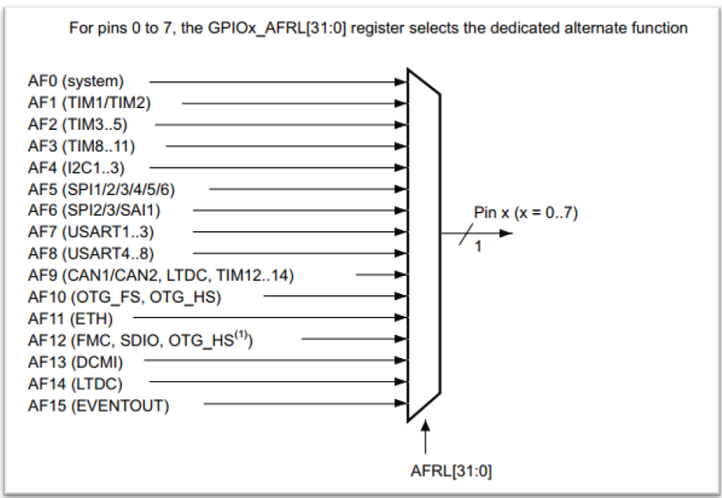

Alternate function

Giới thiệu sơ qua về chức năng Alternate function: Hai thanh ghi (GPIOx_AFRL và GPIOx_AFRH) được cung cấp để chọn một trong số 16 Input/output chức năng thay thế có sẵn cho mỗi I/O. Với các thanh ghi này, bạn có thể kết nối một chức năng thay thế với một số chân khác theo yêu cầu của ứng dụng của bạn.

Ví dụ: để sử dụng chức năng cho pin 0 đến pin 7 bạn sử dụng thanh ghi AFRL, với giá trị tương ứng ảnh thì pin sẽ được kết nối với với chức năng tương ứng. Các chức năng ở đây đây có thể là là: TIMER, I2C, SPI, UART, CAN, USB, ETH…

Các thanh ghi cấu hình cơ bản

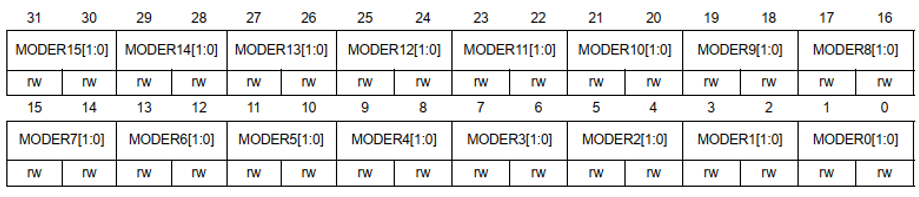

1.GPIO Port mode register (GPIOx MODER)

Giải thích ký hiệu:

- x: port cần cấu hình: A, B, C, D, E, F, I , J, K tùy thuộc mức độ hỗ trợ của dong chip.

- MODERy [1: 0]: y là bit cấu hình cũng như là giá trị tên của pin tương ứng (y = 0..15), mỗi pin sử dụng 2 bit với 4 giá trị có thể cấu hình.

Các bit MODERy [1: 0] được cấu hình theo 4 loại như sau:

- 00: Input (reset state), reset state có thể là 0 hoặc 1 không mặc định trước.

- 01: General purpose output mode, chân Digital IO đơn thuần

- 10: Alternate function mode

- 11: Analog mode, sử dụng cho ADC hoặc DAC

Các bạn để ý lý tự “rw” nghĩa là từng giá trị trong thanh ghi này có thể được đọc và ghi. Trong khi 1 số thanh ghi khác chỉ có thể đọc giá trị “r”.

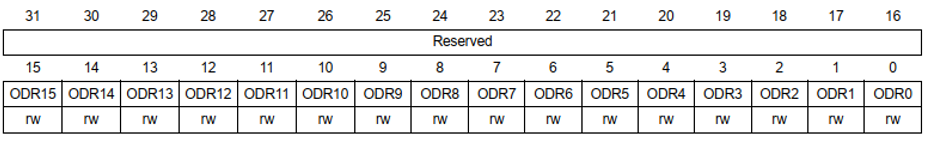

2. GPIO Port output data register (GPIOx ODR)

Bits [31:16] Không sử dụng, phải giữ ở trạng thái mặc định là 0.

Bits [15:0] ODRy: Output data cho chân tín hiệu (y = 0..15). Mức 1 tương ứng với output mức cao và ngược lại mức 0 tương ứng với output mức thấp.

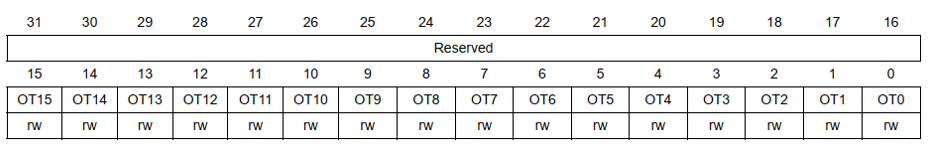

3. GPIO Port output type register (GPIOx OTYPER)

Bits [31:16] Không sử dụng, phải giữ ở trạng thái mặc định là 0.

Bits [15:0] OTy: Kiểu Output cho chân tín hiệu (y = 0..15). Mức 0 tương ứng với Output push-pull và ngược lại mức 1 tương ứng với Output open-drain.

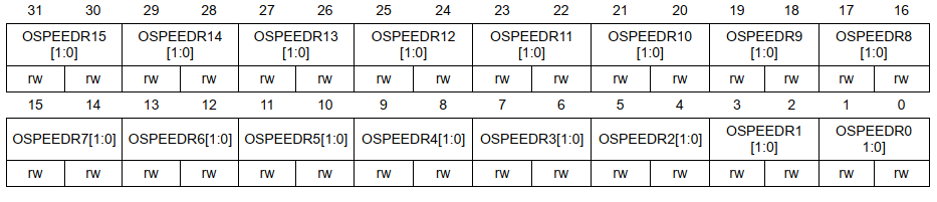

4. GPIO Port output speed register (GPIOx OSPEEDR)

OSPEEDRy[1:0]: pin thứ y (y = 0..15) được config bởi 2 bit tương ứng trong thanh ghi với 4 giá trị:

- 00: Low speed, giá trị này là 2MHz với dòng F407

- 01: Medium speed, giá trị này là 25MHz với dòng F407

- 10: High speed, giá trị này là 50MHz với dòng F407

- 11: Very high speed, giá trị này là 100MHz với dòng F407

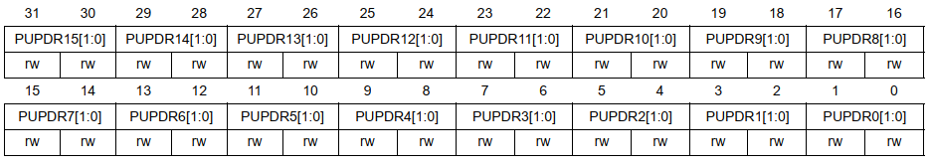

5. GPIO Port pull-up/pull-down register (GPIOx PUPDR)

PUPDRy[1:0]: pin thứ y (y = 0..15) được config bởi 2 bit tương ứng trong thanh ghi với 4 giá trị:

- 00: Không dùng pull-up, pull-down

- 01: Pull-up

- 10: Pull-down

- 11: Không dùng, không cấu hình.

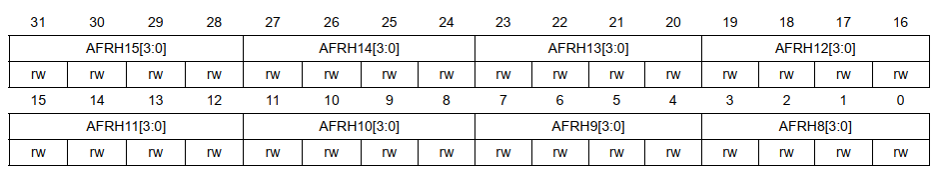

5. GPIO Port alternate function register (GPIOx AFRL và GPIO AFRH)

Tôi lấy ví dụ với thanh ghi GPIOx_AFRL:

AFRLy: Alternate function pin thứ y (y = 0..15) được config bởi 4 bit cho mỗi pin, tương ứng trong thanh ghi với 15 giá trị tưng ứng từ AF0 đến AF15:

0000: AF0

…

1111: AF15

Còn một số thanh ghi khác giúp cấu hình và đọc/ghi giá trị GPIO, các bạn tham khảo thêm trong Reference Manual của nhà sản xuất.

Một số ví dụ mẫu cài đặt thanh ghi để cấu hình chân GPIO

- Cấu hình Chân 0 GPIOA hay chân PA0 ở chế độ ouput push -pull max speed 50MHz :

GPIOA->CRL=(3<<0) ;

- Cấu hinh chân PB0, PB1, PB2, PB3 output push-pull max speed 50 MHz:

GPIOB->CRL=(3<<0)|(3<<4)|(3<<8)|(3<<12);

- Cấu hình chân PA0,PA1,PA2 input floating

GPIOA->CRL =(4<<0)|(4<<4)|(4<<8);

- Cấu hinh chân PA0,PA1,PA2 input pull down

GPIOA->CRL=(8<<0)|(8<<4)|(8<<8);

- Các chân 7,8,9 của Port C được cấu hình ouput push pull, xuất ra mức điện áp cao(3.3V):

GPIOC->ODR = (1<<7)|(1<<8)|(1<<9);

GPIOC->BSRR=(1<<7)|(1<<8)|(1<<9);

- Để đưa chân này về mức điện ấp thâp( 0V):

GPIOC->CRL &= ~((8<<0)|(8<<4)|(8<<8));

GPIOC->BSRR =(1<<23)|(8<<24)|(8<<25);

- Giả sử đọc trang thái chân PB5 và giá trị đọc được lưu vào biến a:(a có giá trị 1 nếu chân tương ưng có mức điện áp cao còn a=0 thì ngược lại)

uint8_t a;

a=((GPIOB->IDR&(1<<5))>>4);

- Giả sử đọc trang thái chân PA6 và giá trị đọc được lưu vào biến a:

uint8_t a;

a=((GPIOA->IDR&(1<<6))>>5);

Tạm Kết

Tới đây là kết thúc của phần bài viết về lý thuyết GPIO với STM32F4, tuy hơi phức tạp nhưng đây là tiền để cho phần thực hành về GPIO lần sau, mời bạn cùng đón đọc.